### Features

Fout = 32.768 kHz

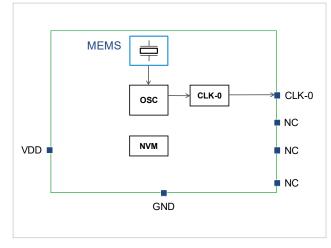

**Block Diagram**

- Frequency stability of ±20 ppm

- Small Oscillator Footprint: 1.32 mm<sup>2</sup>

1.2 x 1.1 mm QFN

- Ultra-low power: 510 nA typical

- Supply voltage: 1.35 V to 1.98 V

- Operating temperature range: from -10°C to +85°C

- Pb-free, RoHS and REACH compliant

# Applications

- Wearables and Hearables

- Health and wellness monitors

- Gaming and remote controllers

- AR/VR headsets

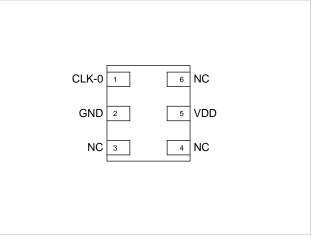

# 1.2 x 1.1 mm Package Pinout

Figure 2. Pin Assignments (Top view) (Refer to Table 4 for Pin Descriptions)

Figure 1. Block Diagram

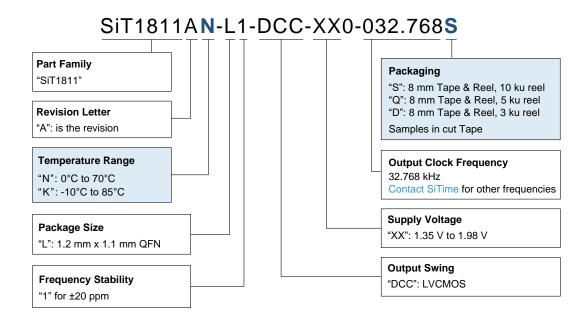

# **Ordering Information**

### TABLE OF CONTENTS

| Features                      |     |

|-------------------------------|-----|

| Applications                  | . 1 |

| Applications<br>Block Diagram | . 1 |

| 1.2 x 1.1 mm Package Pinout   | . 1 |

| Ordering Information          | . 2 |

| Electrical Characteristics    | . 4 |

| Layout Guidelines             | . 8 |

| Anufacturing Guidelines       | . 8 |

| Revision History              | . 9 |

## **Electrical Characteristics**

### Table 1. Electrical Characteristics

Conditions: Min/Max limits are over temperature, V<sub>DD</sub> = 1.35 - 1.98 V, unless otherwise stated.

Typical are at 25°C and  $V_{DD} = 1.8$  V.

| Parameter                              | Symbol                          | Min. | Тур.              | Max.          | Unit              | Condition                                                                                                                                                                      |

|----------------------------------------|---------------------------------|------|-------------------|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        |                                 |      | Frequency a       | nd Stability  |                   |                                                                                                                                                                                |

| Output Frequency                       | Fout                            |      | 32.768            |               | kHz               | 32.768 kHz Output. Contact SiTime for other frequencies                                                                                                                        |

| Initial Frequency Tolerance            | F_tol                           | -20  | -                 | +20           | ppm               | Includes 2x reflow, at 25°C                                                                                                                                                    |

| Frequency Stability <sup>[1],[2]</sup> | F_stab                          | -20  | -                 | 20            | ppm               | Over temperature, $V_{DD}$ , aging @25°C, and 20% load variation. Temperature Ordering Codes N and K only.                                                                     |

|                                        |                                 |      | Jitter Perf       | ormance       |                   |                                                                                                                                                                                |

| Integrated Phase Jitter                | IPJ                             | _    | 3                 | 9             | ns <sub>RMS</sub> | $F_{OUT}$ = 32 kHz. Integration bandwidth = 100 Hz to<br>16 kHz. Inclusive of 50 mV peak-to-peak<br>sinusoidal noise on V <sub>DD</sub> . Noise frequency 100 Hz<br>to 20 MHz. |

| RMS Period Jitter                      | PJ                              | -    | 2.5               | 8             | ns <sub>RMS</sub> | Cycles = 10,000, f = 32.768 kHz. Per JEDEC standard 65B                                                                                                                        |

|                                        |                                 | Sup  | ply Voltage and C | urrent Consum | nption            |                                                                                                                                                                                |

| Operating Supply Voltage               | V <sub>DD</sub>                 | 1.35 | -                 | 1.98          | V                 | Ordering Code: XX. Contact SiTime for 1.2V operation.                                                                                                                          |

| No Load Supply Current                 | IDD                             | -    | 510               | 635           | nA                | Fout = 32.768 kHz, VDD = 1.8 V;<br>Operating Range: -10°C to 85°C                                                                                                              |

| Start-up Time at Power-up              | t_start                         | -    | _                 | 115           | ms                | Measured when supply reaches 90% of final $V_{\text{DD}}$ to the first output pulse.                                                                                           |

|                                        |                                 |      | Output Char       | acteristics   |                   |                                                                                                                                                                                |

| Output Rise/Fall Time                  | t <sub>R</sub> , t <sub>F</sub> |      | 20                | 40            | ns                | 15 pF load, 20% to 80% of $V_{DD}$ for LVCMOS.<br>20% to 80% of $V_{OH}$ for Reduced Swing outputs.<br>Factory Programmable Rise/Fall times. Contact<br>SiTime for details.    |

| Output Clock Duty Cycle                | DC                              | 45   | _                 | 55            | %                 |                                                                                                                                                                                |

|                                        |                                 |      | LVCMOS            | Output        | -                 |                                                                                                                                                                                |

| Output Voltage High                    | VOH                             | 90%  | _                 |               | V <sub>DD</sub>   | $I_{OH} = -1 \ \mu A$<br>Contact SiTime for reduced swing options                                                                                                              |

| Output Voltage Low                     | VOL                             | -    | _                 | 10%           | V <sub>DD</sub>   | I <sub>OL</sub> = 1 μA<br>Contact SiTime for reduced swing options                                                                                                             |

|                                        |                                 |      | Operating Temp    | erature Range | )                 |                                                                                                                                                                                |

| Operating Temperature                  | Op_Temp                         | 0    | _                 | +70           | °C                | Ordering Code (N); can support ±20 ppm stability                                                                                                                               |

| Range                                  |                                 | -10  | -                 | +85           | °C                | Ordering Code (K); can support ±20 ppm stability                                                                                                                               |

|                                        |                                 |      |                   |               |                   |                                                                                                                                                                                |

Notes:

Tested with Agilent 53132A frequency counter. Measured with ≥100 ms gate time for accurate frequency measurement.

Total stability over temperature includes Initial Frequency Tolerance and Frequency Stability.

### Table 2. Absolute Maximum Ratings

Attempted operation outside the absolute maximum ratings may cause permanent damage to the part. Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

| Parameters                                  | Test Conditions      | Value       | Unit |

|---------------------------------------------|----------------------|-------------|------|

| Continuous Power Supply Voltage Range (VDD) |                      | -0.5 to 2.2 | V    |

| Human Body Model (HBM) ESD Protection       | JESD22-A114          | 2000        | V    |

| Charge-Device Model (CDM) ESD Protection    | JESD22-C101          | 500         | V    |

| Latch-up Tolerance                          | JESD78 Compliant     |             |      |

| Mechanical Shock Resistance                 | Mil 883, Method 2002 | 20,000      | g    |

| Mechanical Vibration Resistance             | Mil 883, Method 2007 | 70          | g    |

| Max Junction Temperature                    |                      | 130         | °C   |

| Storage Temperature                         |                      | -65 to 150  | °C   |

### Table 3. Package Characteristics

| Package (mm x mm) | θ-JA (K/W) | θ-JB (K/W) | θ-JC (K/W) | Ψ-JT (K/W) <sup>[3]</sup> |

|-------------------|------------|------------|------------|---------------------------|

| 1.2 x 1.1         | 206        | 85         | 148        | 14                        |

Note: 3. Refer to SiTime AN23033 application note.

### Table 4. Pin Configuration

| Pin | Symbol | I/O                 | Functionality                                                                                                                                              |

|-----|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CLK-0  | Out                 | Oscillator Clock Output                                                                                                                                    |

| 2   | GND    | Power Supply Ground | Connect to Ground                                                                                                                                          |

| 3   | NC     | NC                  | No Connect                                                                                                                                                 |

| 4   | NC     | NC                  | No Connect                                                                                                                                                 |

| 5   | VDD    | Power Supply        | Device supply voltage. Under normal operating conditions, VDD does not require external<br>bypass/decoupling capacitor(s). Includes on-chip VDD filtering. |

| 6   | NC     | NC                  | No Connect                                                                                                                                                 |

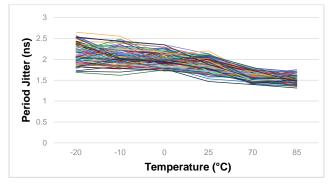

# **Typical Performance Plots**

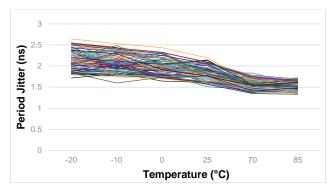

Figure 3. Period Jitter, no supply noise over temperature for VDD = 1.5 V

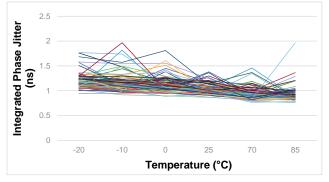

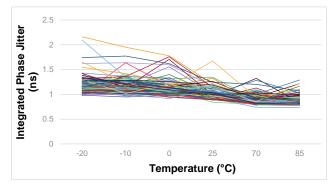

Figure 5. Integrated Phase Jitter, no supply noise over temperature for VDD = 1.5 V

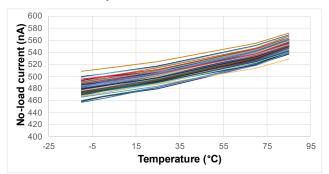

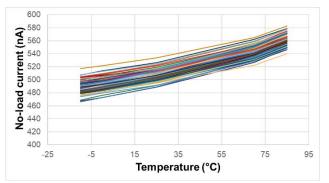

Figure 7. Typical No-load current over temperature for VDD = 1.5 V

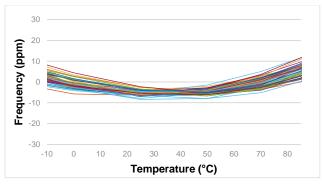

Figure 9. Frequency Vs Temp Stability

Figure 4. Period Jitter, no supply noise over temperature for VDD = 1.8 V

Figure 6. Integrated Phase Jitter, no supply noise over temperature for VDD = 1.8 V

Figure 8. Typical No-load current over temperature for VDD = 1.8 V

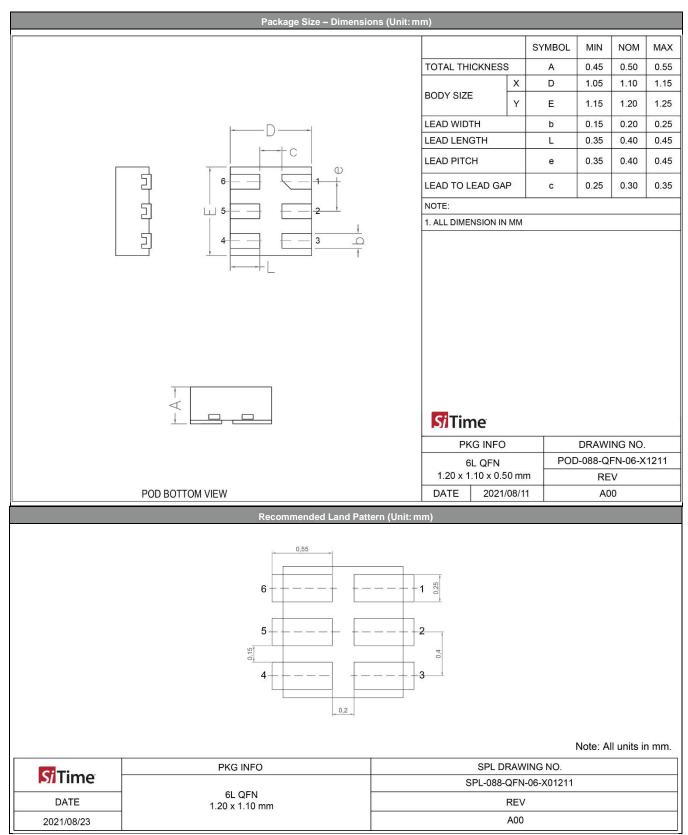

## **Dimensions and Patterns**

### Layout Guidelines

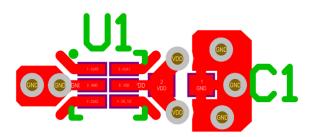

Sample PCB layout is shown in the following figure. It is strongly recommended that the PCB designer observe the following layout guidelines:

- Do not connect any of the pads directly to a copper polygon or a wide PCB trace. This may cause bad solder joints due to non-uniform heating transfer during the assembly process

- Provide short length (>0.5 mm) and thin width (≤0.25 mm) traces to each pad and then to the respective copper polygon or wide trace

- Keep mirror symmetry of the traces X-Y planes. This will prevent the rotation effect during reflow

- Keep high-current and high-speed traces away from the oscillator

- Route high edge-rate and noisy signals at least 1 mm away from clock-out and pin1 signal traces

- The use of orthogonal routes is **recommended** to avoid signal coupling

Figure 10. SiT1811 Layout example for board without bypass capacitor

Figure 11. SiT1811 Layout example for board with bypass capacitor

It is recommended to connect VDD and GND pins with polygons or thick wires to corresponding layers of the board. For GND connection it would apply for both device and bypass connections.

For additional layout recommendations, refer to the Best Design Layout Practices.

### **Manufacturing Guidelines**

The is a precision timing device. Proper PCB solder and cleaning processes must be followed to ensure best performance and long-term reliability.

For additional manufacturing guidelines and marking/ tape-reel instructions, refer to SiTime Manufacturing Notes.

### **Revision History**

#### Table 5. Revision History

| Version | Release Date | Change Summary                                                                                                                                                                                                                                                                                                                                  |

|---------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1     | 18-Jun-2021  | Advance Datasheet                                                                                                                                                                                                                                                                                                                               |

| 1.0     | 22-Feb-2024  | Added details to current consumption. Max current increased at 85°C. Add plots for key parameters such as stability over temp, current consumption over temp for 1.5 V and 1.8 V operating voltage, Period Jitter, etc. Removed ordering option for low voltage (1.2 V) and also ±50 ppm Added SiTimeDirect and other links, formatting updates |

#### SiTime Corporation, 5451 Patrick Henry Drive, Santa Clara, CA 95054, USA | Phone: +1-408-328-4400 | Fax: +1-408-328-4439

© SiTime Corporation 2021-2024. The information contained herein is subject to change at any time without notice. SiTime assumes no responsibility or liability for any loss, damage or defect of a Product which is caused in whole or in part by (i) use of any circuitry other than circuitry embodied in a SiTime product, (ii) misuse or abuse including static discharge, neglect or accident, (iii) unauthorized modification or repairs which have been soldered or altered during assembly and are not capable of being tested by SiTime under its normal test conditions, or (iv) improper installation, storage, handling, warehousing or transportation, or (v) being subjected to unusual physical, thermal, or electrical stress.

Disclaimer: SiTime makes no warranty of any kind, express or implied, with regard to this material, and specifically disclaims any and all express or implied warranties, either in fact or by operation of law, statutory or otherwise, including the implied warranties of merchantability and fitness for use or a particular purpose, and any implied warranty arising from course of dealing or usage of trade, as well as any common-law duties relating to accuracy or lack of negligence, with respect to this material, any SiTime product and any product documentation. This product is not suitable or intended to be used in a life support application or component, to operate nuclear facilities, in military or aerospace applications, or in other mission critical applications where human life may be involved or at stake. All sales are made conditioned upon compliance with the critical uses policy set forth below.

#### CRITICAL USE EXCLUSION POLICY

BUYER AGREES NOT TO USE THIS PRODUCT FOR ANY APPLICATION OR IN ANY COMPONENTS: USED IN LIFE SUPPORT DEVICES, TO OPERATE NUCLEAR FACILITIES, FOR MILITARY OR AEROSPACE USE, OR IN OTHER MISSION-CRITICAL APPLICATIONS OR COMPONENTS WHERE HUMAN LIFE OR PROPERTY MAY BE AT STAKE.

For aerospace and defense applications, SiTime recommends using only Endura™ ruggedized products.

SiTime owns all rights, title and interest to the intellectual property related to SiTime's products, including any software, firmware, copyright, patent, or trademark. The sale of SiTime products does not convey or imply any license under patent or other rights. SiTime retains the copyright and trademark rights in all documents, catalogs and plans supplied pursuant to or ancillary to the sale of products or services by SiTime. Unless otherwise agreed to in writing by SiTime, any reproduction, modification, translation, compilation, or representation of this material shall be strictly prohibited.