Quad PLL, Netzwerksynchronisator mit 12 Ausgängen

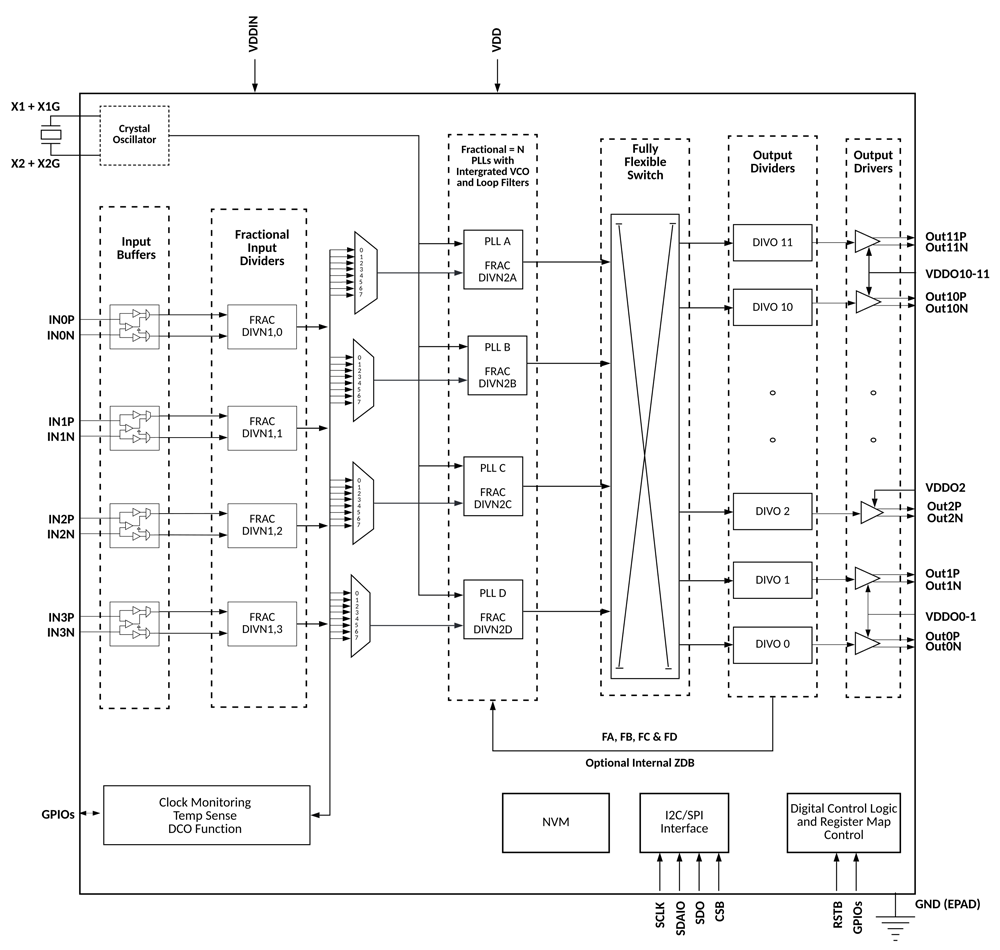

LoginDer Netzwerksynchronisierer SiT95316 bietet eine programmierbare vierfache fraktionierte Frequenzumsetzung mit flexiblen Optionen für die Frequenzumsetzung von Eingang zu Ausgang. Die Hochleistungs-DPLLs unterstützen bis zu 4 differenzielle oder 8 Single-Ended-Eingangstakte und bieten 12 Taktausgänge. Die Taktausgänge können völlig flexibel von jeder der 4 PLLs abgeleitet werden. Dieses Gerät ist vollständig programmierbar mit der I2C/SPI-Schnittstelle oder einem On-Chip-einmal programmierbaren (OTP) nichtflüchtigen Speicher für werkseitig vorprogrammierte Geräte.

Don’t waste time shipping samples. Request demo & test parts remotely in our lab and qualify for your design today.

Wir sind bereit, Ihnen zu helfen!

Bitte füllen Sie das untenstehende Formular aus und jemand wird sich mit Ihnen in Verbindung setzen. Elemente, die mit einem gekennzeichnet sind * sind erforderlich.

| "Spezifikationen" | "Value" |

|---|---|

| Operating Temperature Range (°C) | -40 to 85 |

| Package Type (mm²) | 9x9 mm, 64-pin QFN |

| Number of Inputs | 4 |

| Number of Outputs | 12 |

| Input Type | LVCMOS, LVDS, LVPECL, CML |

| Input Frequency Range | 0.5 Hz to 2.1 GHz (Differential) |

| Output Type | LVPECL, CML, HCSL, LVDS, LVCMOS |

| Output Frequency Range | 0.5 Hz to 2.94912 GHz (Differential) |

| Number of PLL/Clock Domains | 4 PLL |

| Phase Jitter (rms) | 85 fs typ.; 70 fs typ. (with MEMS oscillator) |

| Repeatable Input-Output Delay | ±225 ps |

| Frequency Control DCO | 0.001 ppt (all outputs) |

| Phase Control DCO | <1 ps (all outputs) |

| Internal ZDB Mode | <0.5 ns input to output delay variation |

| Programmability | NVM OTP, External EEPROM, Partial autonomous, SPI/I2C |

| Features | Wander attenuation loop bandwidth down to 0.09 mHz, ±25 ps maximum phase hit, JESD204B/C support |

| Availability | Production |

-

64-pin 9x9 mm QFN Clock Generators - Network Synchronizers - Jitter Cleaners package

- Erstklassiger integrierter Jitter von 85 fs / 70 fs für Quad-PLL

- JESD204B/C-Unterstützung für Datenkonverter-Takte

- 1 PPS-Eingabe-/Ausgabeunterstützung mit der besten Sperrzeit ihrer Klasse unter 20 Sekunden

- Beste stoßfreie Schaltleistung ihrer Klasse mit 25 PS Treffer

- Externe EEPROM-Unterstützung und On-Chip-OTP

- Frequenz-DCO (0,001 ppt) und Phasensteuerungs-DCOs (1 ps Auflösung)

- Interne ZDB auf allen PLLs mit ±500 ps Eingangs-Ausgangsverzögerung über die Temperatur

- G.8273.2 / IEEE 1588 unterstützter Holdover

- Unabhängiger VDDO (3,3 / 2,5 / 1,8 V)

- Vollständig flexibler Ausgangs- und Eingangsmultiplexer

- Ethernet

- Taktung des optischen Transportnetzwerks (OTN) für Framer, Mapper und Prozessoren

- Mikrowellen-Backhaul

- 100G / 200G / 400G / 800G Ethernet

- Drahtlose Netzwerke

- Kleine Zellen

- Speicher, Server und Rechenzentren

- SONET/SDH Stratum 3

- Testen und Messen

- Video übertragen

| Resource Name | Resource Type | Date | Format | Size |

|---|