四路 PLL、12 输出网络同步器

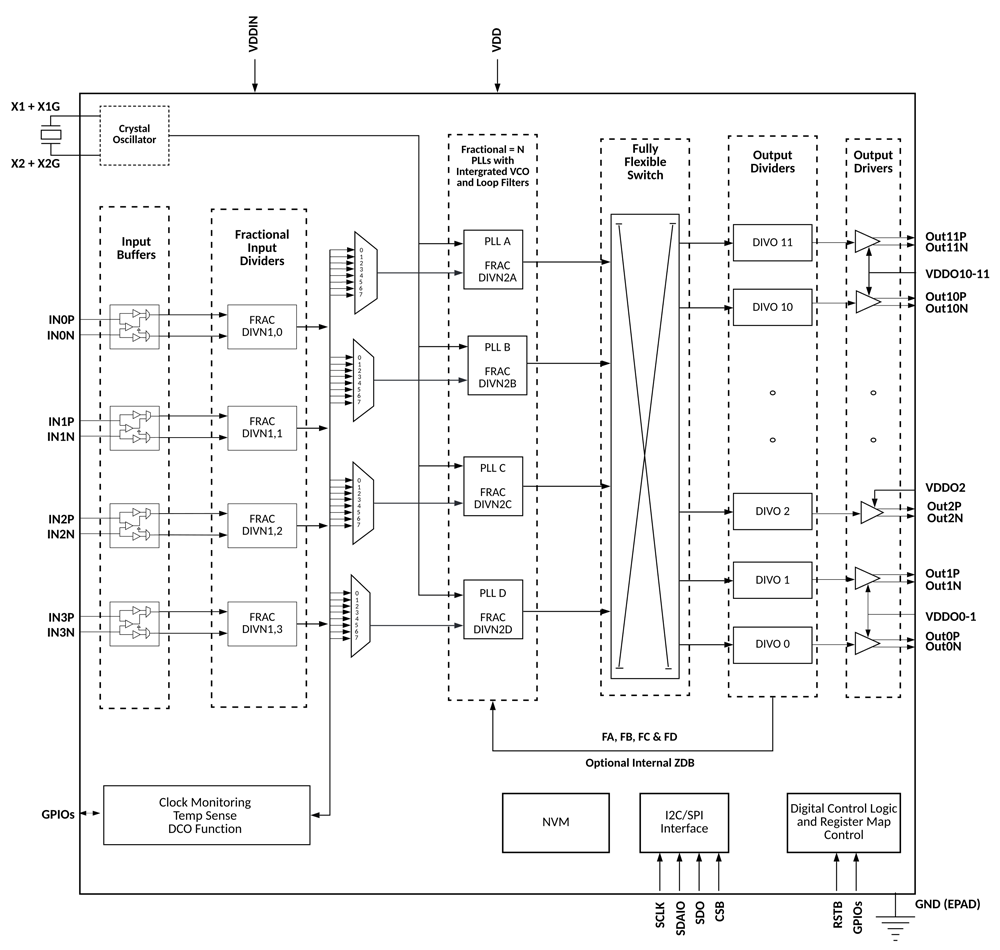

LoginSiT95316 网络同步器提供可编程四分数频率转换,具有灵活的输入到输出频率转换选项。高性能 DPLL 支持多达 4 个差分或 8 个单端输入时钟,并提供 12 个时钟输出。时钟输出可以以完全灵活的方式从 4 个 PLL 中的任何一个获得。该器件可通过 I2C/SPI 接口或工厂预编程器件的片上一次性可编程 (OTP) 非易失性存储器进行完全编程。

| "眼镜" | "Value" |

|---|---|

| Operating Temperature Range (°C) | -40 to 85 |

| Package Type (mm²) | 9x9 mm, 64-pin QFN |

| Number of Inputs | 4 |

| Number of Outputs | 12 |

| Input Type | LVCMOS, LVDS, LVPECL, CML |

| Input Frequency Range | 0.5 Hz to 2.1 GHz (Differential) |

| Output Type | LVPECL, CML, HCSL, LVDS, LVCMOS |

| Output Frequency Range | 0.5 Hz to 2.94912 GHz (Differential) |

| Number of PLL/Clock Domains | 4 PLL |

| Phase Jitter (rms) | 85 fs typ.; 70 fs typ. (with MEMS oscillator) |

| Repeatable Input-Output Delay | ±225 ps |

| Frequency Control DCO | 0.001 ppt (all outputs) |

| Phase Control DCO | <1 ps (all outputs) |

| Internal ZDB Mode | <0.5 ns input to output delay variation |

| Programmability | NVM OTP, External EEPROM, Partial autonomous, SPI/I2C |

| Features | Wander attenuation loop bandwidth down to 0.09 mHz, ±25 ps maximum phase hit, JESD204B/C support |

| Availability | Production |

-

64-pin 9x9 mm QFN Clock Generators - Network Synchronizers - Jitter Cleaners package

- 针对四 PLL 的一流 85 fs / 70 fs 集成抖动

- JESD204B/C 支持数据转换器时钟

- 1 PPS 输入/输出支持,具有低于 20 秒的一流锁定时间

- 一流的无中断切换性能,命中 25 ps

- 外部 EEPROM 支持和片上 OTP

- 频率 DCO (0.001 ppt) 和相位控制 DCO(1 ps 分辨率)

- 所有 PLL 上的内部 ZDB 在整个温度范围内具有 ±500 ps 输入到输出延迟

- G.8273.2 / IEEE 1588 辅助保持

- 独立 VDDO(3.3/2.5/1.8V)

- 完全灵活的输出和输入多路复用器

- 以太网

- 用于成帧器、映射器和处理器的光传输网络 (OTN) 时钟

- 微波回程

- 100G/200G/400G/800G以太网

- 无线网络

- 小蜂窝

- 存储、服务器和数据中心

- SONET/SDH 第 3 层

- 测试与测量

- 广播视频

Apply Filters

| Resource Name | Resource Type | Date | Format | Size |

|---|